Blaupunkt SQR39 vyhledávání stanic nic nenajde

Napsal: 17 pro 2019, 08:05

Ahoj,

zprovoznil jsem starší rádio, dlouho nejelo kvůli špatnému displeji a ztracenému kódu.

Nyní funguje, manuální ladění s dobrým příjmem, ovšem pokud nechám vyhledávat stanici, nezastaví se a projížídí celý FM rozsah dokola.

Na snímku příkládám Servisní manuál s obvodem FM přijímače: TDA1574, Demodulátorem: TDA1596, PLL: SDA2121

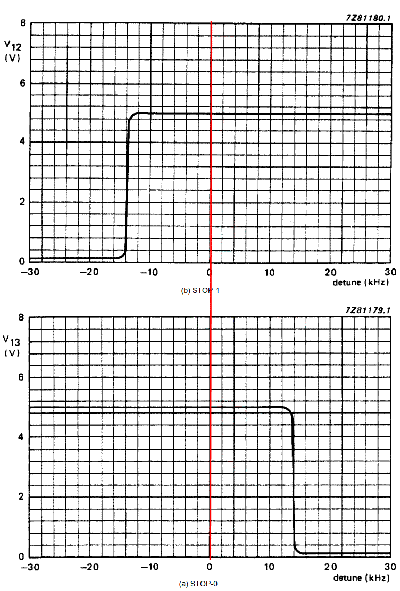

Z data sheetu jsem vyčetl, že TDA1596 indikuje sílu signálu na pinech 12,13.

Tyto jsou přes tranzistor V750 spojeny s piny 6,7,8 na PLL, které jsou dle DataSheetu switche (OUTPUT DRAIN)

Když rádio vyhledávalo stanici,

Měřil jsem hodnoty na Tranzistoru V750 BC548 a na emitoru kolísaly mezi 4,7V a 2V pokud byla anténa zapojená. když jsem ji odpojil, kolísaly výrazně méně asi 4,4V - 4,7V. Domnívám se, že Detekce signálu funguje, ale PLL správně nereaguje na signál z demodulátoru, chápu to správně?

SDA2121 6,7,8 jsou popsány jako OUTPUT DRAIN. Nejsem si jistý, jak fungují a v jakém jejich stavu PLL přestane měnit frekvenci.

Při popsaném experimentu na pinu 6 kolísá 0,05-0,15V pin 7 a 8 jsou 0V

Chápu správně, že by měly být přes Rezistory ukostřeny v ten moment, kdy Demodulátor vyšle signál o silném signálu FM?

zprovoznil jsem starší rádio, dlouho nejelo kvůli špatnému displeji a ztracenému kódu.

Nyní funguje, manuální ladění s dobrým příjmem, ovšem pokud nechám vyhledávat stanici, nezastaví se a projížídí celý FM rozsah dokola.

Na snímku příkládám Servisní manuál s obvodem FM přijímače: TDA1574, Demodulátorem: TDA1596, PLL: SDA2121

Z data sheetu jsem vyčetl, že TDA1596 indikuje sílu signálu na pinech 12,13.

Tyto jsou přes tranzistor V750 spojeny s piny 6,7,8 na PLL, které jsou dle DataSheetu switche (OUTPUT DRAIN)

Když rádio vyhledávalo stanici,

Měřil jsem hodnoty na Tranzistoru V750 BC548 a na emitoru kolísaly mezi 4,7V a 2V pokud byla anténa zapojená. když jsem ji odpojil, kolísaly výrazně méně asi 4,4V - 4,7V. Domnívám se, že Detekce signálu funguje, ale PLL správně nereaguje na signál z demodulátoru, chápu to správně?

SDA2121 6,7,8 jsou popsány jako OUTPUT DRAIN. Nejsem si jistý, jak fungují a v jakém jejich stavu PLL přestane měnit frekvenci.

Při popsaném experimentu na pinu 6 kolísá 0,05-0,15V pin 7 a 8 jsou 0V

Chápu správně, že by měly být přes Rezistory ukostřeny v ten moment, kdy Demodulátor vyšle signál o silném signálu FM?